- 您现在的位置:买卖IC网 > Sheet目录346 > NCP5021MUTXG (ON Semiconductor)IC WHITE LED DVR HV AMB 16-UQFN

�� �

�

NCP5021�

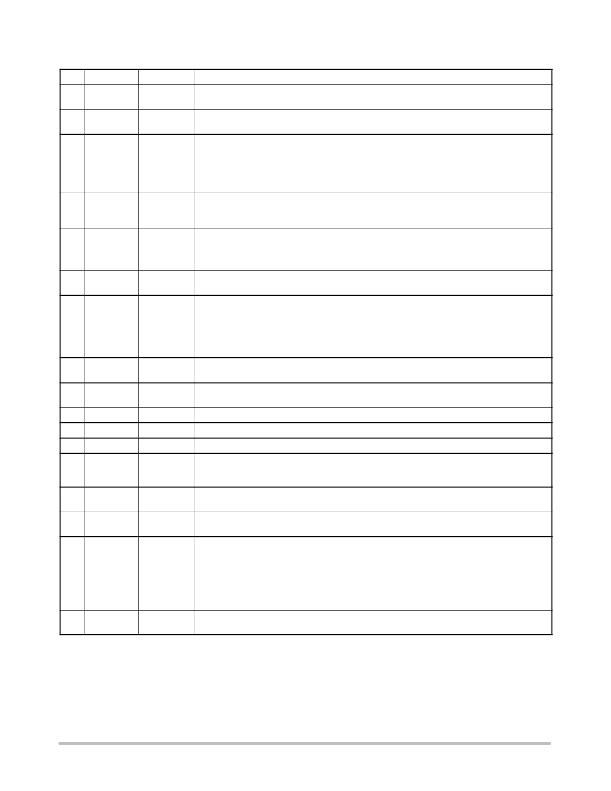

�Table� 1.� PIN� DESCRIPTIONS�

�PIN�

�1�

�2�

�3�

�Name�

�SCL�

�SDA�

�I2CADR�

�Type�

�INPUT,�

�DIGITAL�

�INPUT,�

�DIGITAL�

�INPUT,�

�DIGITAL�

�Description�

�This� pin� carries� the� I2C� clock� to� control� the� DC/DC� converter� and� to� set� up� the� output� current� and�

�the� photo� sensor.� The� SCL� clock� is� associated� with� the� SDA� signal.�

�This� pin� carries� the� data� provided� by� the� I2C� protocol.� The� content� of� the� SDA� byte� is� used� to� pro-�

�gram� the� mode� of� operation� and� to� set� up� the� output� current.�

�This� pin� is� used� to� select� the� I2C� address� of� the� NCP5021:�

�?� I2CADR� =� Low� 3� address� =� %0111� 0010� =� $72�

�?� I2CADR� =� High� 3� address� =� %0111� 0100� =� $74�

�In� order� to� avoid� any� risk� during� the� operation,� the� digital� levels� are� intended� to� be� hardwired� prior� to�

�power� up� the� system.�

�4�

�VSB�

�POWER,�

�OUTPUT�

�This� pin� provides� a� switched� voltage,� derived� from� the� Vbat� supply,� to� bias� the� external� photo� sense.�

�The� current� capability� of� this� voltage� is� 1� mA.�

�The� VSB� pin� is� disconnected� when� the� Shutdown� mode� has� been� engaged.�

�5�

�6�

�7�

�AMBS�

�I� PK�

�I� REF�

�INPUT,�

�ANALOG�

�INPUT,�

�ANALOG�

�INPUT,�

�ANALOG�

�This� pin� senses� the� voltage� developed� across� the� external� Photo� Bias� resistor.� Since� this� is� a� very�

�high� impedance� input,� cares� must� be� observed� to� minimize� the� leakage� current� and� the� noise� that�

�may� influence� the� photo� sense� analog� function.� The� bias� parameters� associated� with� the� AMBS� pin�

�are� reloaded� when� the� chip� resumes� from� Shutdown� to� Normal� operation.�

�This� pin� provides� the� inductor� peak� current� during� normal� operation.� In� no� case� shall� the� voltage� at�

�I� PK� pin� be� forced� either� higher� or� lower� than� the� 1144� mV� provided� by� the� internal� reference.�

�This� pin� provides� the� reference� current,� based� on� the� internal� band� ?� gap� voltage� reference,� to� con-�

�trol� the� output� current� flowing� in� the� LED.� A� 1%� tolerance,� or� better,� resistor� shall� be� used� to� get� the�

�highest� accuracy� of� the� LED� biases.� An� external� current� source� can� be� used� to� bias� this� pin� to� dim�

�the� light� coming� out� of� the� LED.�

�In� no� case� shall� the� voltage� at� I� REF� pin� be� forced� either� higher� or� lower� than� the� 1144� mV� provided�

�by� the� internal� reference.�

�8�

�9�

�10�

�11�

�12�

�13�

�14�

�15�

�16�

�AGND�

�FB�

�NC�

�NC�

�NC�

�Lx�

�PGND�

�VBAT�

�Vos�

�POWER�

�INPUT,�

�ANALOG�

�POWER�

�POWER�

�INPUT,�

�POWER�

�OUTPUT,�

�POWER�

�This� pin� is� the� GROUND� signal� for� the� analog� and� digital� blocks� and� must� be� connected� to� the� sys-�

�tem� ground.� A� ground� plane� is� strongly� recommended.�

�This� pin� is� the� current� sense� of� the� series� arranged� LED.� The� built� ?� in� current� mirror� will� automatic-�

�ally� adapt� the� voltage� drop� across� this� pin� (typically� 400� mV).�

�This� pin� shall� be� left� open� for� normal� operation.�

�This� pin� shall� be� left� open� for� normal� operation.�

�This� pin� shall� be� left� open� for� normal� operation.�

�The� external� inductor� shall� be� connected� between� this� pin� (drain� of� the� internal� Power� switch)� and�

�Vbat.� The� voltage� is� internally� clamped� at� 40� V� under� worst� case� conditions.� The� external� Schottky�

�diode� shall� be� connected� as� close� as� possible� to� this� pin.� See� Note� 1� for� ESR� recommendations.�

�This� pin� is� the� GROUND� reference� for� the� DC/DC� converter� and� the� output� current� control.� The� pin�

�must� be� connected� to� the� system� ground,� a� ground� plane� being� strongly� recommended.�

�Input� Battery� voltage� to� supply� the� analog� ,� the� digital� blocks� and� the� main� Power� switch� driver.� The�

�pin� must� be� decoupled� to� ground� by� a� 10� m� F� ceramic� capacitor.�

�This� pin� senses� the� output� voltage� supplied� by� the� DC/DC� converter.� The� Vos� pin� must� be� by-�

�passed� by� 1.0� m� F/50� V� ceramic� capacitor� located� as� close� as� possible� to� the� pin� to� properly� bypass�

�the� output� voltage� to� ground.� The� circuit� shall� not� operate� without� such� bypass� capacitor� connected�

�to� the� Vos� pin.�

�The� output� voltage� is� internally� clamped� to� 40� V� maximum� in� the� event� of� no� load� situation.�

�NOTE:� Due� to� the� very� fast� dV/dt� transient� developed� during� the� operation,� using� a� low� pass� filter� is�

�strongly� recommended� as� depicted� in� the� schematic� diagram� Figure� 1.�

�NC�

�?�

�Not�

�Connected�

�Back� side� exposed� pad� is� not� internally� connected� and� can� be� either� left� floating� or� connected� to� the�

�system� Ground.�

�1.� Using� low� ESR� ceramic� capacitor� (X5R� or� better)� and� low� ESR� inductor� with� minimum� Eddie� losses� is� mandatory� to� optimize� the� DC/DC�

�efficiency.�

�http://onsemi.com�

�2�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

NCP5050MTTXG

IC LED DRIVR PHOTO FLASH 10-WDFN

NCP5111DR2G

IC DRIVER HI/LOW SIDE HV 8-SOIC

NCP5304DR2G

IC DRIVER HI/LOW SIDE HV 8-SOIC

NCP5355DG

IC DRVR SYNC BUCK MOSF 12A 8SOIC

NCP5359ADR2G

IC MOSFET GATE DVR DUAL 8-SOIC

NCP5359DR2G

IC GATE DRIVER VR11.1/AMD 8-SOIC

NCP5360RMNR2G

IC DRIVER MOSFET 56QFN

NCP5366MNR2G

IC DRIVER MOSFET DFN

相关代理商/技术参数

NCP502ASQ15T1

制造商:ONSEMI 制造商全称:ON Semiconductor 功能描述:80 mA CMOS Low Iq Voltage Regulator in an SC70−5

NCP502ASQ15T1G

制造商:ONSEMI 制造商全称:ON Semiconductor 功能描述:80 mA CMOS Low Iq, Low−Dropout Voltage Regulator

NCP502ASQ18T1

制造商:ONSEMI 制造商全称:ON Semiconductor 功能描述:80 mA CMOS Low Iq Voltage Regulator in an SC70−5

NCP502ASQ18T1G

制造商:ONSEMI 制造商全称:ON Semiconductor 功能描述:80 mA CMOS Low Iq, Low−Dropout Voltage Regulator

NCP502ASQ25T1

制造商:ONSEMI 制造商全称:ON Semiconductor 功能描述:80 mA CMOS Low Iq Voltage Regulator in an SC70−5

NCP502ASQ25T1G

制造商:ONSEMI 制造商全称:ON Semiconductor 功能描述:80 mA CMOS Low Iq, Low−Dropout Voltage Regulator

NCP502ASQ27T1

制造商:ONSEMI 制造商全称:ON Semiconductor 功能描述:80 mA CMOS Low Iq Voltage Regulator in an SC70−5

NCP502ASQ27T1G

制造商:ONSEMI 制造商全称:ON Semiconductor 功能描述:80 mA CMOS Low Iq, Low−Dropout Voltage Regulator